- paging은 오버헤드 많이 발생

- requires a large amount of mapping information

- mapping information은 보통 물리 메모리에 저장되고, 페이징은 논리적으로 프로그램에 의해 생성되는 각 가상 주소에 대한 여분의 메모리를 필요로 한다.

THE CRUX: HOW TO SPEED UP ADDRESS TRANSLATION

--> TLB(Translation - lookaside buffer)

: simply a hardware cache of popular virtual-to-physical address translations

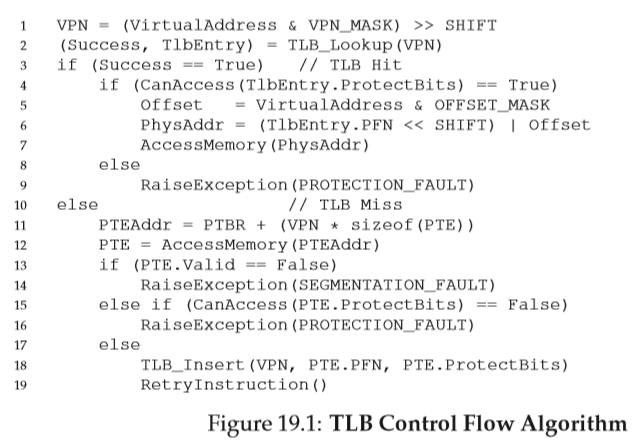

19.1 TLB Basic Algorithm

- TLB 먼저 확인 후,

- 1. success시 line 3이하

- 2. else 시 line 10 이하

- 따라서, TLB miss가 최대한 없어야 good (miss가 많으면 비효율..)

19.2 Example: Accessing An Array

- 10개의 array 공간에 접근할 때, a[0] 때에 TLB miss가 일어나지만, 인접한 a[1]과 a[2]는 TLB hit

- a[3] miss , a[4]~a[6] hit

- a[7] miss, a[8]~a[9] hit

--> 인접한 공간에 의한 효율성 : spatial locality

- 접근 후 바로 다시 접근하면 모든 열 개의 배열 공간이 다 TLB hit

--> 인접한 시간에 의한 효율성 : temporal locality

19.3 Who Handles The TLB Miss?

- 예전 : hardward / 최근 : software

- 하드웨어는 exception만 발생시키고, raises the privilege level to kernel mode, trap handler로 jump

- software-managed appraoch의 장점 : flexibility, simplicity

19.4 TLB Contents: What's In There?

19.5 TLB Issue: Context Switches

THE CRUX: HOW TO MANAGE TLB CONTENTS ON A CONTEXT SWITCH

- One approach is to simply flush the TLB on context switches, thus emptyng it before running the next process.

- However, there is a cost: each time a process runs, it must incur TLB misses as it touches its data and code pages. If the OS switches between processes frequently, this cost may be high.

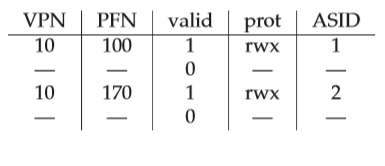

- To reduce this overhead, some systems add hardware support to enable sharing of the TLB across context switches.

|

▶ |  |

- with address-space identifiers(ASID), the TLB can hold translations from different processes at the same time without any confusion.

-출처-

<OPERATING SYSTEMS three easy pieces>

REMZI H. ARPACI-DUSSEAU

ANDREA C. ARPACI-DUSSEAU

UNIVERSITY OF WISCONSIN-MADISON

'CS > 운영체제' 카테고리의 다른 글

| 18. Paging: Introduction (0) | 2019.12.10 |

|---|---|

| 17. Free-Space Management(2) (0) | 2019.12.10 |

| 17. Free-Space Management(1) (1) | 2019.11.23 |

| 16. Segmentation (0) | 2019.11.23 |

| 15. Mechanism: Address Translation (0) | 2019.11.10 |

댓글